为了满足当今电子产品的需求,数字电路的速度变得越来越快。高速设计曾经是一个冷门的电子产品领域,但如今,大多数产品至少会有一部分需要 “高速设计”。这些设计要求设计师按照高速规则和要求布置电路板;而对部分设计师来说,这是一个全新的领域。为此,本文总结了一些最常见的高速

为了满足当今电子产品的需求,数字电路的速度变得越来越快。高速设计曾经是一个冷门的电子产品领域,但如今,大多数产品至少会有一部分需要 “高速设计”。这些设计要求 PCB 设计师按照高速规则和要求布置电路板;而对部分设计师来说,这是一个全新的领域。为此,本文总结了一些最常见的高速 PCB 设计准则,希望对您的高速 layout 设计有所助益。

在开始 layout 设计之前,有很多设计和数据库的细节需要事先处理妥当。

虽然在开始设计高速 PCB layout 之前有很多内容需要设置,但大多数人都没有过多地考虑原理图。设计师应该验证元件、仿真电路,并完成设计。但原理图本身是否已经为 layout 准备妥当?如果设计师不能轻松地理解电路的意图,杂乱无序的原理图会让 PCB layout 难上加难。例如,高速信号路径需要按顺序摆放,以便设计者能够在 layout 中模拟器件的位置。标记出希望 layout 团队清楚了解的设计区域也很有帮助。其中包括:

用于高速设计的器件 footprint 必须像 PCB layout 一样进行检查和验证,同时也会涉及一些额外的資料库方面的工作。例如,为了在高频或射频设计中保证信号完整性,可能需要修改使用的 footprint 以减少焊盘尺寸。此外,一些 footprint 可能要缩减到最小尺寸,以适应高密度设计的要求。天行体育官网不过,器件的 footprint 应该尽可能地遵循行业和制造商的规范,以符合可制造性设计 (DFM) 的要求。许多设计工具,如 Cadence Allegro PCB Editor,可以提供在线库浏览功能,用于拉取指定供应商的 footprint 模型。

在开始 layout 设计之前,必须选择用于制造高速电路板的材料。恶劣的工作环境可能需要更坚固的电路板结构,需要使用材料的物理特性来计算受控阻抗布线:

●FR-4 的介电常数可能无法保持所需要的阻抗值,或者导致设计出现超出可接受范围的信号损失。

PCB 器件也需要由制造商进行审查和确认。鉴于当下的供应链问题,需要确保在开始设计之前有可用的元件。

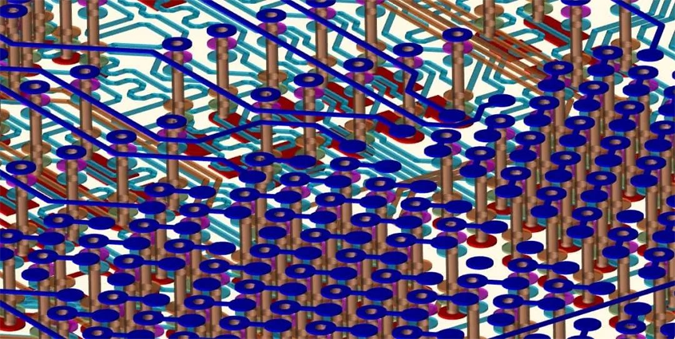

高速设计需要特定的板层堆叠,以便实现 EMI 屏蔽和信号完整性。首先要考虑在内部层纳入一个完整、连续的接地平面。许多电路板在整个电路板堆叠上还设置了多个接地平面层,用于微带线或带状线配置中的多层传输线布线。板层堆叠需要在 PCB CAD 数据库中建立,也可从外部来源导入。在这方面,如果 PCB 设计系统能够与供应商直接沟通来交换堆叠信息,则会十分有帮助,如下面的视频所示:

PCB 设计系统通常有一套非常全面的设计规则和约束条件,可以针对设计进行设置。标准的电路板设计使用器件和网络类来指定间距规则、走线宽度、过孔和其他约束。对于高速设计,应该设置一套全新的规则,包括:

可以为每个设计设置这些规则;或者在许多情况下,从另一个 layout 中导入,以减轻设计师的工作量。

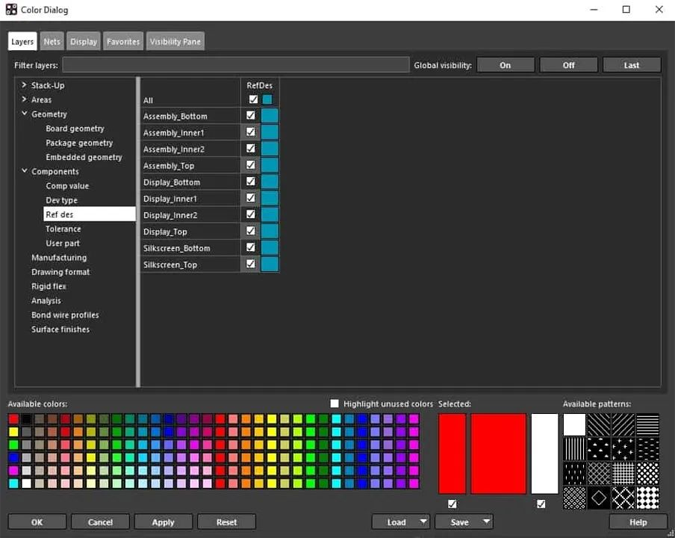

设置的最后一项是参数。参数非常重要,包括显示参数,如颜色和填充模式、网格、布线偏好和其他一系列参数。通过管理这些参数,设计师可以提高使用工具时的效率。

高速设计的器件摆放依然需要与标准设计摆放遵循相同的规则。为了平衡起见,元件应均匀地分布在电路板周围,而且需要遵循制造和测试设计规则(DFM 和 DFT)。其中包括器件与其他元件、电路板特征和电路板边缘的间距。高温运行的器件应集中在一起,以尽可能多地利用电路板上的区域来散热,并且必须注意不能阻碍空气在电路板上的流动。连接器和其他人机接口元件应摆放在技术人员容易接触到的地方,不同的电源应相互分散放置。

高速设计的不同之处在于,它需要在整个设计中实现最佳的信号完整性。信号完整性的主要部分取决于接地平面上有清晰的信号返回路径,以及确保数字和模拟电路彼此分离。因此,除了要支持所需的走线布线外,器件摆放还必须确保清晰的信号返回路径和电路隔离。为了完成这种复杂的器件摆放,通常最好是在电路板上布置实际元件之前进行布图规划。布图规划有助于划分电路的功能分区,同时不需要不断地移动元件。

前文提到,在制定器件摆放计划的同时,应一同规划电源分配网络 (PDN)。接下来,我们来了解一些 PDN 的设计建议。

在高速电路板中,精心设计 PDN 对电路板的最终电气性能至关重要。如果没有清晰的信号返回路径,电路板可能会产生大量的噪声,导致产生错误的信号,干扰电路的正常运行。还可能导致其他信号完整性问题,如 EMI 和接地反弹。在参考平面上找不到清晰返回路径的返回信号,最终可能会耦合到任何它们可以找到的返回路径上,其中也包括其他走线。这种无意的耦合将产生共模电流,共模电流可能会产生电磁辐射,并带来额外的噪声。

●在对高速传输线进行布线时,确保它们在相邻的接地平面上有一条清晰的信号返回路径。在较高的速度和频率下,会自然而然地在走线周围形成返回路径,因此很容易规划。

●在一个集中的区域内有太多的过孔、电路板切口或其他障碍物,会破坏参考平面上的清晰返回路径。

●处理器、存储器和其他大引脚数的高密度器件使用许多电源引脚来满足其巨大的电源需求。

●在这些连接中,每一个连接都需要一个尽可能靠近电源引脚的旁路电容,以获得最佳的电源滤波效果。

当电路板上的器件布置妥当时,设计将有一个基本的模板,表明走线应该如何布置。不过需要注意,我们很可能仍然要移动元件,以完善和调整布线——就像在任何 PCB 设计中一样。

●确保充分遵循线长、匹配长度、宽度、间距、层、受阻抗控制的布线参数、差分对、走线调整和过孔分配的设计规则和约束条件。

●不要在接地平面的空隙或断开处布线。这可能会破坏信号的清晰返回路径,并有可能造成前面讨论的信号完整性问题。

●当对高速信号进行布线时,要确保它们在相邻的接地平面上有一个清晰的信号返回路径。

●对于敏感的信号(如时钟线和差分对),确保它们与其他布线之间留有额外的间隙,通常是标准走线宽度的三倍。

●确保将高速传输线布设到它们被分配的层上,以保证它们在相邻参考平面上的返回路径。

●避免通过高速传输线改变层的属性,但如果非要这样做,要尽量使它们与同一接地平面相邻,以获得信号返回路径。如果层的过渡段比层对更远,就在信号过孔旁边使用一个接地过孔作为返回路径的过渡。

●注意层与层之间垂直方向的串扰,其间距可能比同一层上并排的两条走线要小。

本文列出的高速 PCB 的设计准则远非详尽无遗,但已足够帮助我们开始着手高速 PCB 设计。另外,记得要充分使用 CAD 工具的功能。除了上文已经谈到的设计规则和约束条件外,Cadence PCB 设计工具还有许多其他高效功能助力高速设计,如:

●动态背钻:背钻信息跟随设计,实时更新。设计调整后,无需手动更新背钻信息。

●在设计中,像使用过孔一样使用高速结构(替换、在Constraint Manager中设定)。

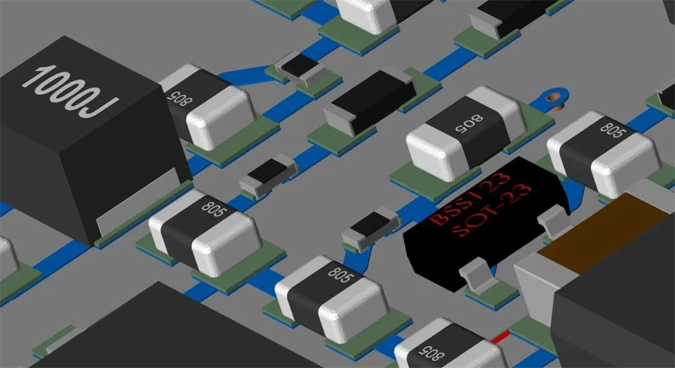

●3D Canvas:让设计者看到PCB实体,眼前展示的是组装完成的PCB。

●Allegro Constraint Compiler:将设计指南转换为设计规则,实现规则同源,帮助设计者快速准确复用规则。